## H/W기반 데이터 가속 카드를 이용한 고속 패킷 처리

조태진 팀장

### AGENDA

배경

고속 패킷 처리 기술

DPU / IPU 소개 및 활용 방안

## 1. 배경

#### 환경의 변화

- 클라우드 확산 및 데이터센터의 데이터양의 증가와 다양한 워크로드의 발생

- \* 데이터센터 트래픽이 2016년 연간 6.0 ZB에서 2021년 19.5 ZB까지, 연평균 27%의 성장률

- 네트워크 보안 요구 수준 향상

- 네트워크 트래픽의 암호화 비중은 점차 증가 → 트래픽 가시성 확보를 위한 암복호화 기능 필요

\*전체 인터넷 트래픽의 암호 트래픽 비중은 63% 웹트래픽의 80% 차지

- 네트워크 보안에 있어 복합적 방어 요구 필요 → 트래픽 검사 등 DPI 기술 활용 필요

\* 위협 정보 검사 및 어플리케이션과 사용자 인지

#### 새로운 요구사항을 충족시키기 위한 고민

- CPU만으로 요구되는 성능의 달성이 어려움

- 워크로드의 일부를 CPU가 아닌 다른 프로세서로 옮겨 유연하게 배치 → 전체 시스템 성능 향상

데이터 처리의 변화에 따른 새로운 아키텍처 필요

## 2. 고속 패킷 처리 기술

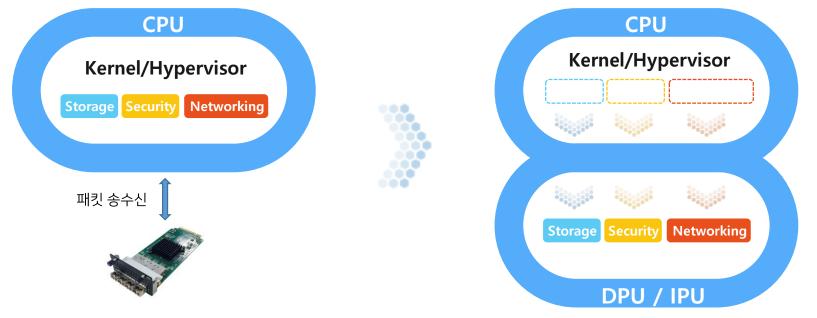

네트워크 카드는 트래픽 송수신에서 인프라를 위한 데이터 처리 장치로 발전

- 데이터 처리의 이동

- 클라우드 확산 및 데이터센터의 데이터양의 방대화로 고성능 컴퓨팅 기술 필요

- CPU 만으로의 처리 한계 → 워크로드 성능을 네트워크 위치에서 가속 처리를 통해 확보

- 네트워크 카드의 진화

일반 NIC

- Ethernet ASIC으로 구성

- 패킷 송수신 및 흐름 제어

Intel, Broadcom 등 다양

HPC용 특수 NIC

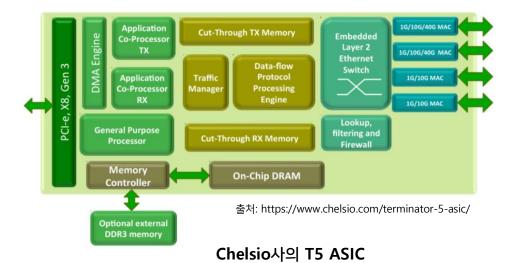

출처: https://www.chelsio.com/terminator-5-asic/

- NIC 및 다수의 가속기로 구성된 SoC

- 패킷 프로세싱

- 세션 관리 등의 복합적인 기능

Chelsio, Napatec, Mellanox 등

#### FPGA이용 SmartNIC

- NIC + FPGA

- 패킷 송수신 및 흐름제어

- FPGA를 이용 필요 기능을 구현하여 하드웨어적인 처리가 가능 Intel, Xilinx

#### DPU / IPU

출처: https://www.nvidia.com/kokr/networking/products/data-processing-unit

- FPGA+CPU, 가속SoC+CPU, 가속SoC+GPU+CPU

- 다양한 반도체의 기능과 CPU를 이용하여 IT인프라내 다앙한 기능 처리 **Nvidia, Intel, Xilinx**

Techtonic 2021

## 2. 고속 패킷 처리 기술

HPC용 특수 NIC을 이용한 네트워크 처리

#### HPC용 특수 NIC

- ❷ ASIC 기반 오프로딩 처리

- 네트워크 처리를 위한 패킷 처리 엔진 내장

- 패킷 Flow 엔진을 통한 카드단에서의 세션 처리

- ToE, RDMA등 H/W 기반 가속을 통한 CPU 로드 분산

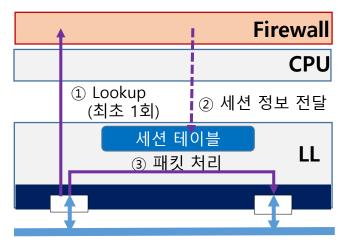

#### 적용 사례

☑ 패킷 지연 최소화

- 네트워크 카드에 트래픽의 세션 정보를 보유

- 트래픽 세션 정보를 통해 트래픽을 CPU로 전달하지 않고 직접 전송

- CPU 처리 대비 패킷의 지연 시간을 50µs → 1µs 으로 전송

- 지연 시간이 중요한 주식 거래 등의 금융부분에 도입하여 운용

## 2. 고속 패킷 처리 기술

FPGA를 이용한 SmartNIC의 주요 기능 및 적용 사례

#### SmartNIC 주요 기능

#### ❷ 프로그래밍 가능한 NIC

- 워크로드의 일부를 FPGA를 이용한 NIC으로 오프로딩하고 Host에서 제어하여 성능 향상

- FPGA를 통해 변화하는 네트워킹 프로토콜에 맞춰 기능을 업데이트하여 대응

- 인텔 및 Xilinx FPGA를 주로 사용하며 카드단에서의 패킷 처리로 CPU 효율을 높여 저전력 시스템 구현

#### 적용 사례

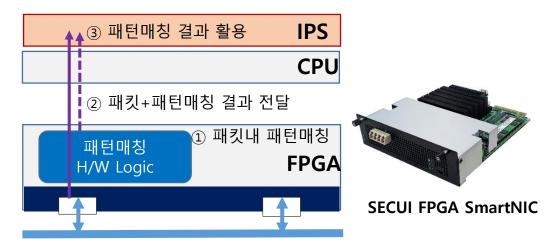

#### ♥ DPI 오프로딩

- DPI 기술에 필요한 패턴매칭을 FPGA내에 프로그래밍 가능 회로로 구현

- 20Gbps 트래픽에 대해 IPS의 정책의 패턴이 포함되었는지 검사

- CPU로 검사 결과와 패킷을 전달

- IPS는 검사 결과를 활용하여 정상적인 패킷은 검사 우회하여 성능 향상

프로세서 + H/W 가속 칩 또는 FPGA를 활용한 데이터 처리 CPU의 S/W에서 처리하던 워크로드를 NIC에 위치한 프로세서 기반 가속칩과 연동하여 처리 효율 향상

#### **NVIDIA DPU**

- Data Processing Unit

- BlueFiled 칩 기반 가속(ARM + H/W Acceleration)

- Security 가속 엔진 기반 보안 처리 가속

- IPsec, RegEx, Connection tracking

- NG Firewall, IDS/ IPS, DDoS Prevention

- 2 x 10/25/50/100Gb 인터페이스 제공

#### KEY SOFTWARE-DEFINED, HARDWARE-ACCELERATED **APPLICATIONS**

출처:https://www.nvidia.com/content/dam/en-zz/Solutions/Data-Center/documents/datasheet-nvidia-bluefield-2-dpu.pdf

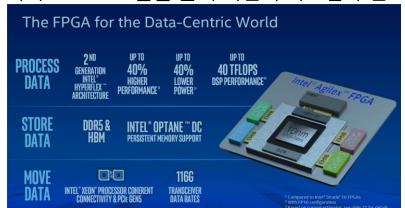

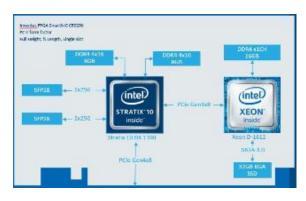

#### **INTEL IPU**

- ✓ Infrastructure Processing Unit

- INTEL Xeon + FPGA 기반 가속 처리

- Xeon을 이용한 S/W 호환성 및 FPGA를 활용한 기능구현의 유연성 제공

- Xeon에 내장된 Crypto 엔진을 이용한 암복호화 제공

- 다양한 멀티 포트 구성 가능(10G ~ 100G)

출처:https://allinfo.space/2021/06/15/ipu-instead-of-dpufpgascpus-with-smartnic-from-intel-for-the-data-center/

#### DPU / IPU를 활용한 데이터 센터에서의 활용

- 데이터센터의 CPU 효율을 높이기 위해 네트워크 카드단에서의 가속 처리 필요

- Host에서 수행하던 프로세스들에 대해 오프로드 처리(네트워크 가상화 + 저장장치 가속 + 암호화)

- 주요 업체 솔루션: NVIDIA DPU, 인텔 IPU

- 프로세서(NVIDIA: ARM, 인텔: Xeon) + H/W 가속칩(ASIC, FPGA) 구조

\* NVIDIA의 경우 AI 처리를 위한 별도 GPU 장착 가능

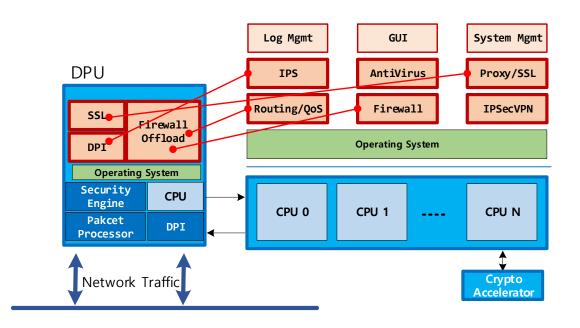

#### DPU를 활용한 방화벽 Offload 사례

- DPU내에 Flow를 관리하는 테이블을 보유하여 정책에 따라 오프로딩 처리하여 성능 개선

- 보안검사의 유용성 여부를 판단하여 검사가 필요치 않는 트래픽에 대해 우회 처리(ex: 동영상, 게이밍 등)

#### IPU를 활용한 OvS 구현 사례

- 일반적인 NIC을 사용하는 경우 S/W 기반으로 OvS를 구현: CPU의 많은 코어 점유

- OvS 기능을 IPU에 구현하여 CPU 사용률을 1/10까지 줄이고 시스템 전체 성능을 향상

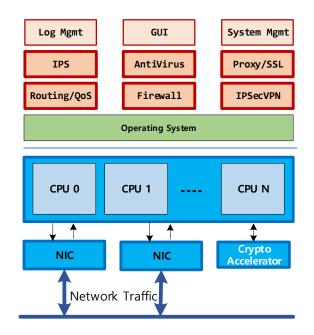

보안 처리 성능 향상을 위한 DPU / IPU 연동

- 네트워크 카드단에서 처리가능한 보안 기능을 사전 수행

- 사전 처리된 보안 처리 결과 및 추가 보안 처리가 필요한 트래픽을 시스템의 CPU에서 처리

NIC의 기능을 단순 패킷 송수신에서 데이터 및 보안 기능을 스스로 처리하는 단계로 진화

# Thank you